Our latest work in the media!

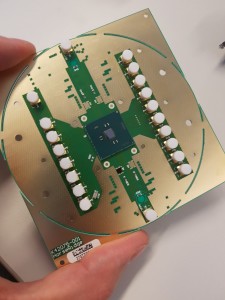

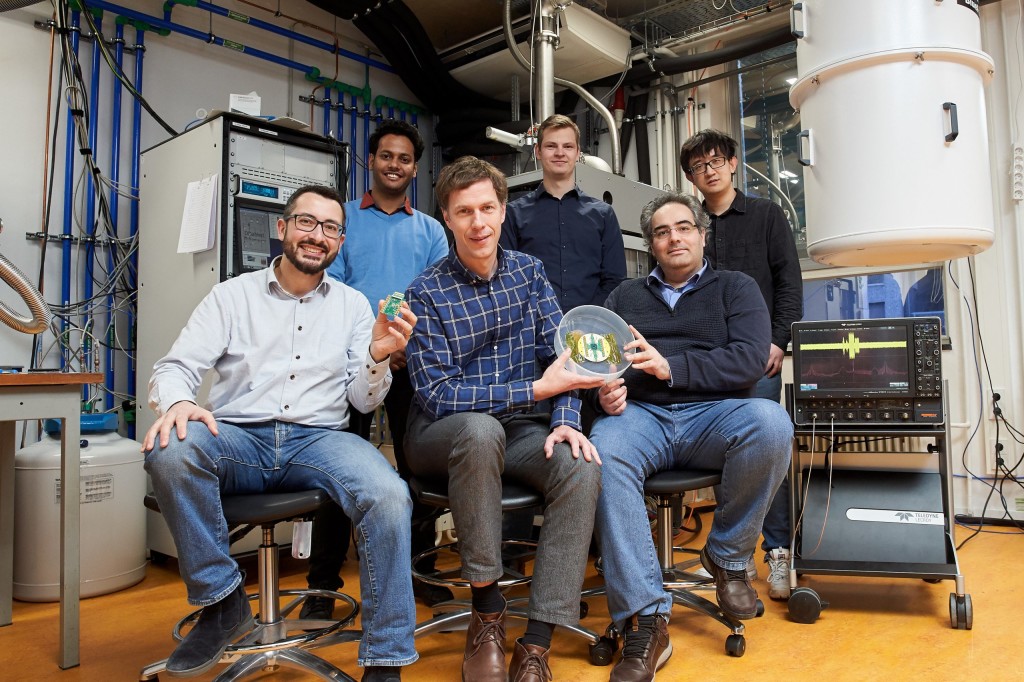

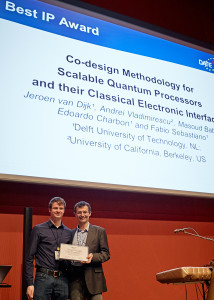

QuTech has resolved a major issue on the road towards a working large-scale quantum computer. Together with Intel, we have designed and fabricated an integrated circuit that can operate at extremely low temperatures when controlling qubits, the essential building blocks of a quantum computer. This paves the way for the crucial integration of qubits and their controlling electronics in the same chip. After our presentation at the International Solid-State Circuit Conference (ISSCC) in San Francisco, the news has spread and has been picked up worldwide by the media.

More information:

- Full press release on QuTech website

- Press release at TU Delft

- Fact sheet

- The announcement on Intel’s website

- In other media

- Phys.org

- De Ingenieur

- The quantum daily

- Federatie van Technologiebranches (FHI)

- DataNews

- Dutch IT Channel

- DataNews

- Executive People

- Engineersonline

- Emerce

- Bits & Chips

- Tweakers

- Techzine

- AG connect

- Techzine BE

- Drimble

- Venture Beat

- Economic Times

- Techerati

- Computing.co.uk

- KitGuru

- HPC Wire

- Dutch Grid Forum

- Techzine.eu

- BCW

- Computer World Italia

- Geeksroom

- Tom’s Hardware

- Notasbit

- Infocity.az

- Investing.com

- Wnp.pl

- Punto informatico

- PClab

- Hardwareluxx

- Iksmedia