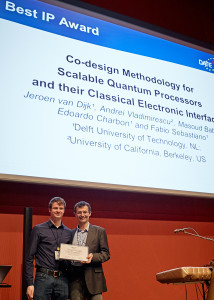

Last week we were awarded the Best IP award at the DATE 2018 (Design Automation and Test in Europe) conference in Dresden!

In this work, we presented, for the first time, a comprehensive methodology to co-design a quantum processor and its electronic interface. As a result, this methodology will enable the design of the electronic interface for scalable quantum computers, i.e. quantum computers with enough power to address relevant practical problems.

A quantum computer fundamentally comprises a quantum processor and the classical controller required to manipulate the quantum bits (qubits). To enable the design of future quantum computers comprising millions of qubits, both the classical electronic and quantum processor must be simultaneously optimized. In the proposed co‐design methodology, qubit performance can be optimized while considering practical trade‐offs in the control circuits, such as power consumption, complexity, and cost. To this end, we have developed SPINE (SPIN Emulator), a toolset enabling the co-simulation of qubits (single‐electron spin qubits in the current implementation) and standard electronics. SPINE can run in Matlab or as a stand-alone C++ application, but also, more interestingly, its VerilogA implementation can be integrated into Cadence, the standard platform for integrated circuit design. As a result, the proposed toolset will be the basis for future electronic designers aiming to build the electronic interface for future scalable quantum computers.

A practical application of this toolset can be found in our new work posted on arXiv: The impact of classical control electronics on qubit fidelity.

The announcement on the DATE website

The paper on the DATE website: