On this website, you will find my resume, a searchable list of my publications and information on my research (under construction). If anything triggers your attention, feel free to contact me.

Latest news

Spring talks on cryo-CMOS

April has come with a cold start of the Spring in The Netherlands, but also with plenty of talks and tutorials on cryo-CMOS. You can see me at:

- ISQED’21 (International Symposium on Quality Electronic Design) on April 8th with the 1-h tutorial Large-Scale Quantum Computers: The need for Cryo-CMOS

- VLSI-TSA (International Symposium on VLSI Technology, Systems and Applications) on April 21st with the invited talk Cryo-CMOS Interfaces for Large-Scale Quantum Computers

- CICC 2021 (Custom Integrated Circuit Conference) on April 25th with the 1.5-h tutorial Cryo-CMOS Electrical Interfaces for Large-Scale Quantum Computers

Due to the on-line or hybrid nature of those events (which allowed me to participate in 2 conferences in US and one in Taiwan within a very short time), those talks have been recorded. So, if you miss them, please let me know and I can send you the video.

ISSCC 2020 Jan van Vessem Award for Oustanding European Paper

Very proud to receive the prestiguious Jan van Vessem Award for the work we presented at ISSCC 2020: ‘A Scalable Cryo-CMOS 2-to-20GHz Digitally Intensive Controller for 4×32 Frequency Multiplexed Spin Qubits/Transmons in 22nm FinFET Technology for Quantum Computers’.

More details about the work here: ‘Cryo-chip overcomes obstacle to large-scale quantum computers’.

Invited talk at IEEE Quantum Week

In the context of IEEE Quantum Week, I have been invited to give a talk at the Workshop on Semiconductor-Inspired Engineering for Quantum Computing. Join (virtually) on Oct.12th to hear about Cryo-CMOS for Silicon Qubits.

Special Session on Quantum Computing at ISCAS 2020

It has been delayed becuase of COVID, but ISCAS 2020 (International Symposium on Circuits and Systems) is finally happenning (virtually) from Oct. 10th to Oct.21st.

Please check out on Oct. 14th the Special Session on Quantum Computers that I co-organized with other colleagues (E.Blokhina, UCD; A. Vladimirescu, UC Berkeley, C. Almudever, TUD).

With talks from UCD (Ireland), EPFL (Switzerland), Aarhus University (Denmark), and Johannes Kepler University Linz (Austria), the session will span several topics and several disciplines as requested to build a complex system as a quantum computer, ranging from quatum device fabrication and operation, thorugh (cryogenic) electrical control, to quantum compilation and quantum algorithms.

A cryo-CMOS controller to overcome obstacles to large-scale quantum computers

Our latest work in the media!

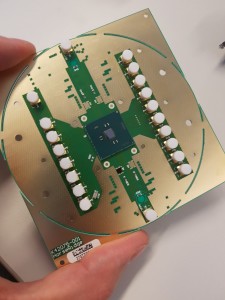

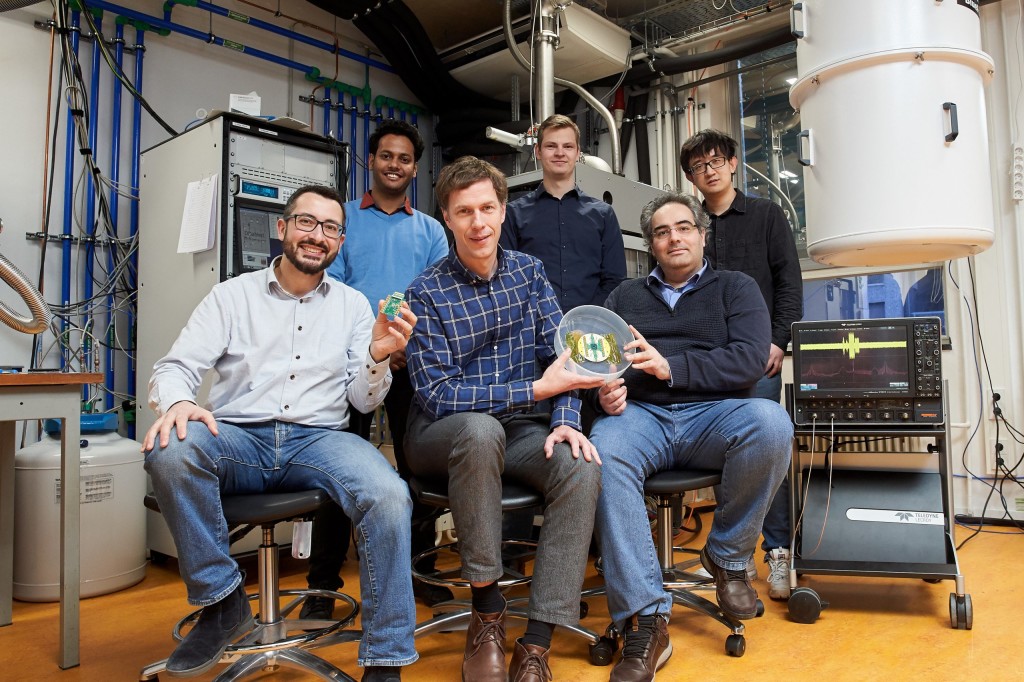

QuTech has resolved a major issue on the road towards a working large-scale quantum computer. Together with Intel, we have designed and fabricated an integrated circuit that can operate at extremely low temperatures when controlling qubits, the essential building blocks of a quantum computer. This paves the way for the crucial integration of qubits and their controlling electronics in the same chip. After our presentation at the International Solid-State Circuit Conference (ISSCC) in San Francisco, the news has spread and has been picked up worldwide by the media.

More information:

- Full press release on QuTech website

- Press release at TU Delft

- Fact sheet

- The announcement on Intel’s website

- In other media

- Phys.org

- De Ingenieur

- The quantum daily

- Federatie van Technologiebranches (FHI)

- DataNews

- Dutch IT Channel

- DataNews

- Executive People

- Engineersonline

- Emerce

- Bits & Chips

- Tweakers

- Techzine

- AG connect

- Techzine BE

- Drimble

- Venture Beat

- Economic Times

- Techerati

- Computing.co.uk

- KitGuru

- HPC Wire

- Dutch Grid Forum

- Techzine.eu

- BCW

- Computer World Italia

- Geeksroom

- Tom’s Hardware

- Notasbit

- Infocity.az

- Investing.com

- Wnp.pl

- Punto informatico

- PClab

- Hardwareluxx

- Iksmedia

2 papers at ISSCC 2020!

We have 2 papers accepted at the next International Solid-State Circuit Conference, the major forum for the presentation of advances in integrated circuits!

We are showing advances in the filed of cryo-CMOS circuits for control of quantum processors. Check them in the advance ISSCC program.

A Scalable Cryo-CMOS 2-to-20GHz Digitally Intensive Controller for 4×32 Frequency Multiplexed Spin Qubits/Transmons in 22nm FinFET Technology for Quantum Computers

B. Patra*1, J. P. G. van Dijk*1, S. Subramanian2, A. Corna1, X. Xue1, C. Jeon2, F. Sheikh2, E. Juarez-Hernandez3, B. Perez Esparza3, H. Rampurawala2, B. Carlton2, N. Samkharadze4, S. Ravikumar2, C. Nieva2, S. Kim2, H-J. Lee2, A. Sammak4, G. Scappucci1, M. Veldhorst1, L. M. K. Vandersypen1,2, M. Babaie*1, F. Sebastiano*1, E. Charbon*2,5, S. Pellerano*2

*Equally-Credited Authors (ECAs)

1Delft University of Technology, Delft, The Netherlands

2Intel, Hillsboro, OR

3Intel, Guadalajara, Mexico

4TNO, Delft, The Netherlands

5EPFL, Neuchatel, Switzerland

A 200dB FoM 4-to-5GHz Cryogenic Oscillator with an Automatic Common-Mode Resonance Calibration for Quantum Computing Applications

J. Gong1, Y. Chen1, F. Sebastiano1, E. Charbon2,3, M. Babaie1

1Delft University of Technology, Delft, The Netherlands

2EPFL, Lausanne, Switzerland

3Intel, Hillsboro, OR

Check the ISSCC 2020 advance program here.

Our paper on the impact of the electronics on a quantum computer is on-line in Phys. Rev. Appl.

Abstract Quantum processors rely on classical electronic controllers to manipulate and read out the state of quantum bits (qubits). As the performance of the quantum processor improves, nonidealities in the classical controller can become the performance bottleneck for the whole quantum computer. To prevent such limitation, this paper presents a systematic study of the impact of the classical electrical signals on the qubit fidelity. All operations, i.e., single-qubit rotations, two-qubit gates, and readout, are considered, in the presence of errors in the control electronics, such as static, dynamic, systematic, and random errors. Although the presented study could be extended to any qubit technology, it currently focuses on single-electron spin qubits, because of several advantages, such as purely electrical control and long coherence times, and for their potential for large-scale integration. As a result of this study, detailed electrical specifications for the classical control electronics for a given qubit fidelity can be derived. We also discuss how qubit fidelity is affected by the limited performance of the general-purpose room-temperature equipment typically employed to control the few qubits available today. Ultimately, we show that tailor-made electronic controllers can achieve significantly lower power, cost, and size, as required to support the scaling up of quantum computers.

Webinar for SSCS on June 27th on Cryo-CMOS

Coming Thursday, June 27th, at 10:00 AM ET, I’ll give a webinar on “Cryogenic CMOS Interfaces for Large-Scale Quantum Computers”. The webinar is organized by the IEEE Solid-State Circuit Society and you can register to attend here.

There will be the opportunity to ask questions. I hope many of you will join!

New “News and views” article in Nature electronics

My article in the “News and views” section of Nature Electronics has just been published on-line. You can find it freely available here: https://rdcu.be/bG4sI.

In this piece, titled “Scalable read-out schemes for qubits“, I comment on the latest results by Dr. Fernando Gonzalez-Zalba at Hitachi Cambridge Laboratory on selective DRAM-like readout of spin qubits (also published in Nature Electronics). I give my views on current state-of-the-art on electronic interfaces for solid-state quantum processors and outline the path that electrical and Quantum Engineers will have to follow to give birth to scalable quantum computers.

Two Cryo-CMOS papers at ESSCIRC/ESSDERC 2019

The work of two of my Ph.D. students has been accepted for presentation at the coming ESSCIRC/ESSDERC conferences to be held in Krakow, Poland next September. Congratulations to Job and Pascal!

Job’s work is showing how to build a voltage reference in standard CMOS that can operate over the whole ultra-wide temperature range from 4 K to 300 K. And, for the first time, we are showing significant statistical data demonstrating the accuracy of such references down to cryogenic temperature.

In the other paper by Pascal, we focus on device characterization of CMOS transistors at cryogenic temperature. We extend our prior work on cryo-CMOS mismatch by showing the characterization of transistor mismatch over a wide range of operating regimes, from strong inversion down to weak inversion. In particular, weak inversion operation is very relevant as it allows for low-power operation, as required in several power-limited cryogenic applications, such as quantum computing.

Both papers will be presented on the first day of the conference, on Tuesday morning and afternoon. See here.

References:

- Job van Staveren, Carmina Garcia Almudever, Giordano Scappucci, Menno Veldhorst, Masoud Babaie, Edoardo Charbon, Fabio Sebastiano, “Voltage References for the Ultra-Wide Temperature Range from 4.2K to 300K in 40-nm CMOS,” to be presented at ESSCIRC 2019.

- Pascal A. ‘T Hart, Masoud Babaie, Edoardo Charbon, Andrei Vladimirescu, Fabio Sebastiano, “Subthreshold Mismatch in Nanometer CMOS at Cryogenic Temperatures,” to be presented at ESSDERC 2019.